Prepared By Mr. EBIN PM, Chandigarh University, Punjab

| REG: AX, BX, CX, DX, DI, SI, BP, SP.<br>SREG: DS, ES, SS, CS.<br>memory: [BX], [BX+SI+7], 16 bit variable, etc<br>immediate: 5, -24, 3Fh, 10001101b, etc | SREG: DS, ES, SS, (except CS).<br>memory: [BX], [BX+SI+7], 16 bit variable, etc |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| • It is very important to do equal number of <b>PUSHs</b> and <b>POPs</b> , otherwise the stack maybe corrupted and it will be impossible to return to operating system. |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| • As you already know we use <b>RET</b> instruction to return to operating system, so when program starts there is a return address in stack (generally it's 0000H).     |

| • <b>PUSH</b> and <b>POP</b> instruction are especially useful because we don't have too much registers to operate with, so here is a trick:                             |

| Store original value of the register in stack (using <b>PUSH</b> ).                                                                                                      |

| ➤Use the register for any purpose.                                                                                                                                       |

| ➢Restore the original value of the register from stack (using POP).                                                                                                      |

| Prepared By Mr. EBIN PM, Chandigarh University, Punjab EDULINE 13                                                                                                        |

| Example: |                                                               |      |   |

|----------|---------------------------------------------------------------|------|---|

|          | ORG 100h                                                      |      |   |

|          | MOV AX, 1234h<br>PUSH AX ; store value of AX in stack.        |      |   |

|          | MOV AX, 5678h ; modify the AX value.                          |      |   |

|          | POP AX ; restore the original value of AX.                    |      |   |

|          | RET                                                           |      |   |

|          | END                                                           |      |   |

|          |                                                               |      |   |

|          | Prepared By Mr. EBIN PM, Chandigarh University, Punjab EDULIN | NE 1 | 4 |

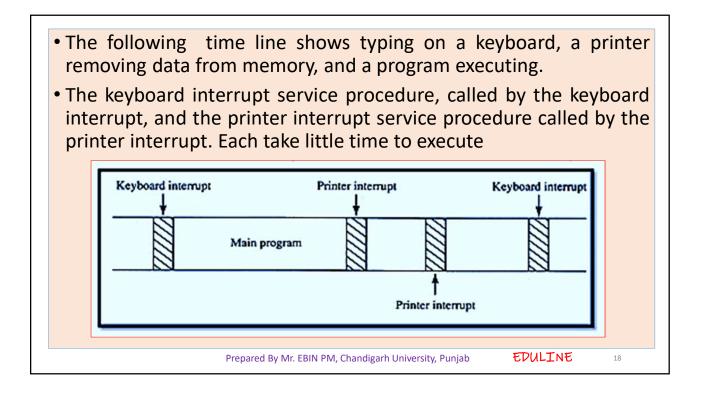

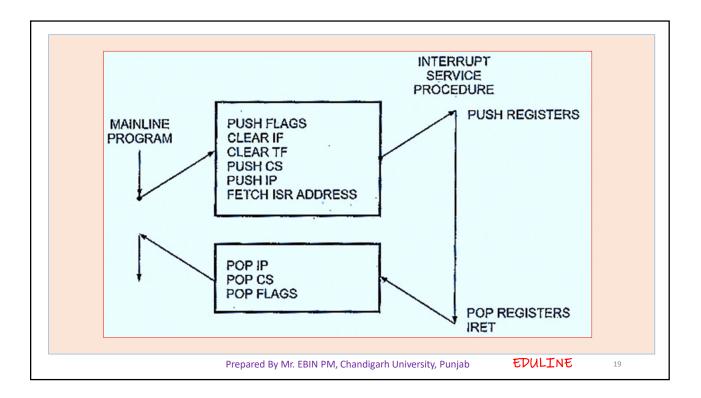

- It decrements stack pointer by 2 and pushes the flag register on the stack.

- It disables the INTR interrupt input by clearing the interrupt flag in the flag

- It resets the trap flag in the flag register.

- It decrements stack pointer by 2 and pushes the current code segment register contents on the stack.

- It decrements stack pointer by 2 and pushes the current instruction pointer contents on the stack.

- It does an indirect far jump at the start of the procedure by loading the CS and IP values for the start of the interrupt service routine (ISR).

- An IRET instruction at the end of the interrupt service procedure returns execution to the main program.

Prepared By Mr. EBIN PM, Chandigarh University, Punjab

EDULINE

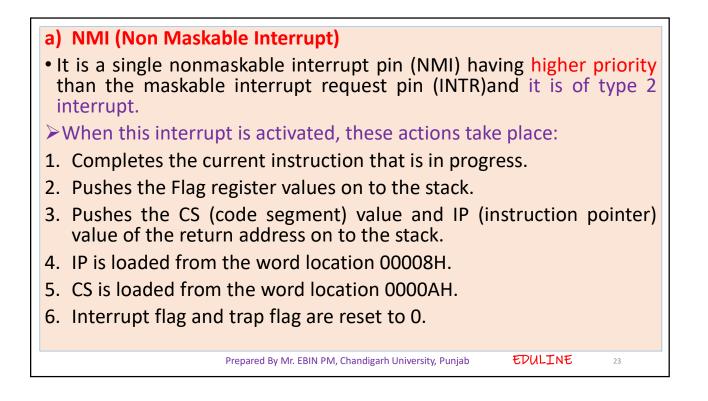

- NMI is a nonmaskable interrupt input pin which means that any interrupt request at NMI input cannot be masked or disabled by any means.

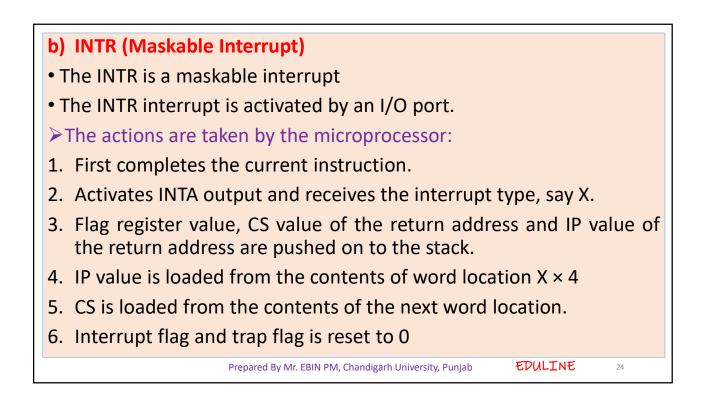

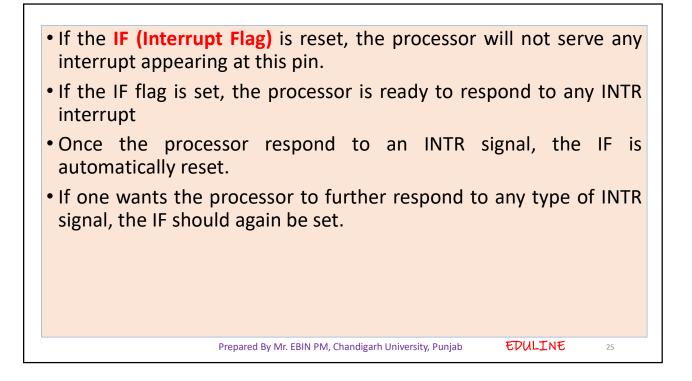

- The INTR interrupt may be masked using the Interrupt Flag (IF)

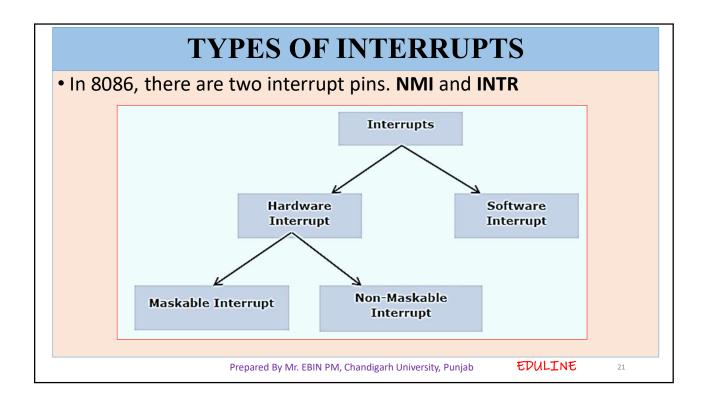

## Hardware Interrupts

- Hardware interrupts are those interrupts which are caused by any peripheral device by sending a signal through a specified pin to the microprocessor.

- The 8086 has two hardware interrupt pins, i.e. NMI and INTR. NMI is a non-maskable interrupt and INTR is a maskable interrupt having lower priority. One more interrupt pin associated is INTA called interrupt acknowledge.

Prepared By Mr. EBIN PM, Chandigarh University, Punjab

EDULINE

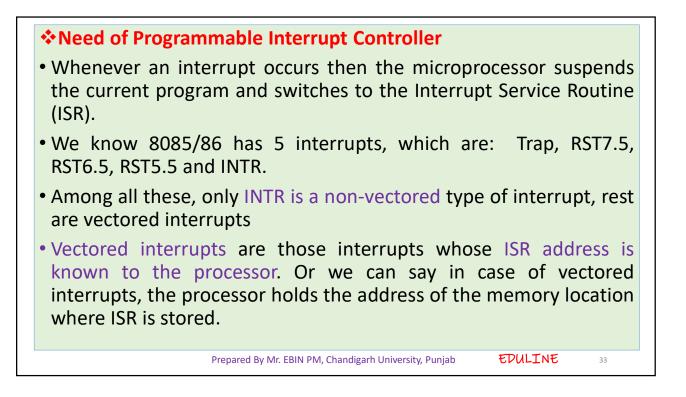

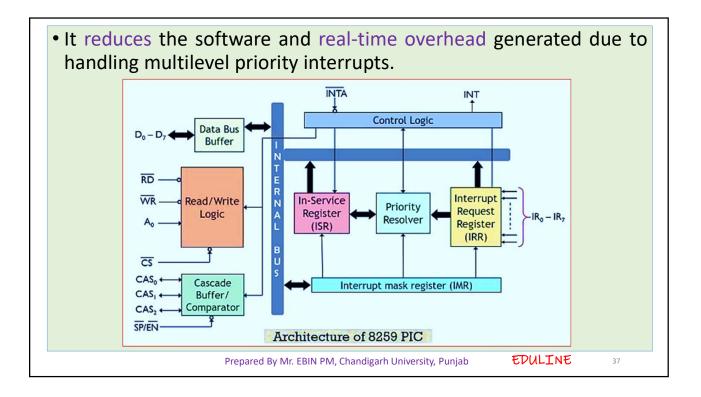

- The processor holds the address of ISR in case of vectored interrupts. So, it is not possible to combine a non-vectored interrupt with a vectored one.

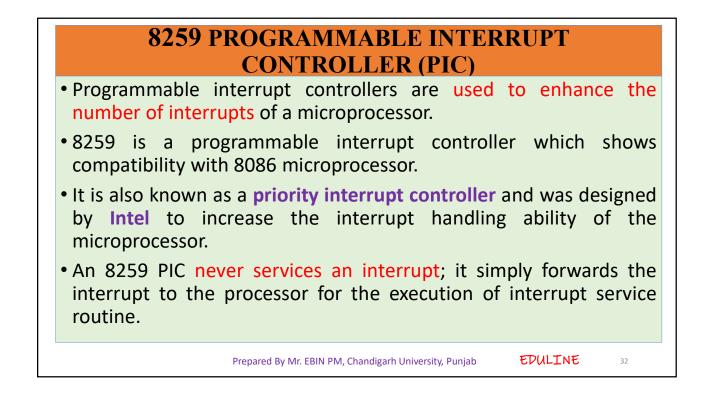

- 8259 is used to combine various interrupts which are non-vectored in nature.

- If the processor gets two INTR signals at the same time but how does the processor get to know that from where the interrupt is generating and where to send the INTA in order to have the ISR address.

- This shows the necessity of 8259. The programmable interrupt controller tells the microprocessor about the interrupt. Basically the external devices initially interrupt the 8259 and further the 8259 interrupts the microprocessor.

```

Prepared By Mr. EBIN PM, Chandigarh University, Punjab

```

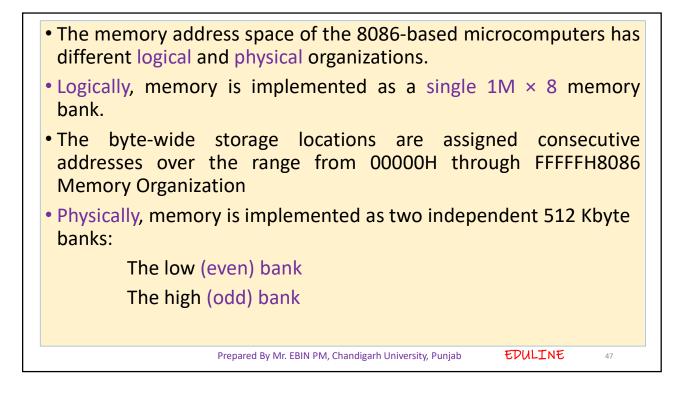

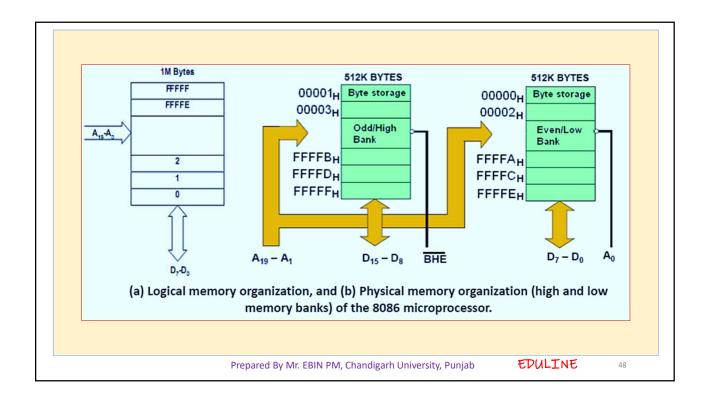

| BHE | A | -   |                                     |

|-----|---|-----|-------------------------------------|

| 0   |   | 0   | Function                            |

| 0   | 0 | ) ( | hoose both odd and even memory bank |

| 0   | 1 | . 0 | Choose only odd memory bank         |

| 1   | 0 | ) ( | Choose only even memory bank        |

| 1   | 1 | L N | lone is chosen                      |

EDULINE

51

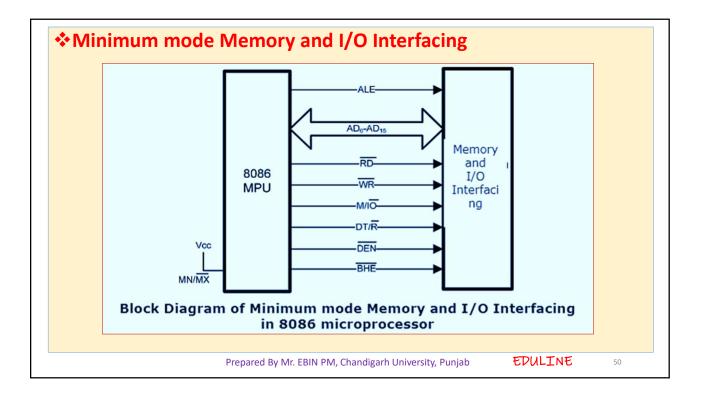

- The control signals provided to support the interface to the memory subsystem are ALE, M/IO, DT/R, RD, WR, DEN and BHE

When Address latch enable (ALE) is logic 1 it signals that a valid address is on the bus.

This address can be latched in external circuitry on the 1-to-0 edge of the pulse at ALE.

M/IO (memory/IO) and DT/R tells external circuitry whether a memory or I/O transfer is taking place over the bus, and whether the 8086 will transmit or receive data over the bus.

The bank high enable (BHE) signal is used as a memory enable signal for the most significant byte half of the data bus, D8 through D15.

- The signals WR (write) and RD (read) identify that a write or read bus cycle is in progress.

• DEN (data enable), is also supplied. It enables external devices to supply data to the microprocessor Maximum mode Memory Interface I/O device IORC I/O device JOWC CLKO Alowo Bus ALE ntroller 8288 DT/R Sn-S DEN 8086 I/O interface circuitry AD0-AD15 RHF MN/MX Ē I/O device EDULINE Prepared By Mr. EBIN PM, Chandigarh University, Punjab 52

| <ul> <li>In maximum mode the 8086 not directly provides all control signal<br/>to support the memory interface.</li> </ul> |

|----------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Instead, an external Bus Controller (8288) provides memory<br/>commands and control signals</li> </ul>            |

|                                                                                                                            |

|                                                                                                                            |

|                                                                                                                            |

|                                                                                                                            |

| Prepared By Mr. EBIN PM, Chandigarh University, Punjab EDULINE 53                                                          |